## 25 GHz Inductorless VCO in a 45 GHz SiGe Technology

Namdar Saniei\*, Hormoz Djahanshahi† and C. Andre T. Salama\*

\* Edward S. Rogers Sr. Department of Electrical & Computer Engineering

University of Toronto

10 King's College Road, Toronto, ON, M5S 3G4, Canada

Email: salama@vrg.utoronto.ca

† PMC-Sierra, Inc.

8555 Baxter Place, Burnaby, BC, V5A 4V7, Canada

**Abstract** — This paper discusses the design and implementation of a 25 GHz VCO in a 45 GHz SiGe process. The VCO is based on a full-wave rectification frequency-doubling technique applied to a 13 GHz differential ring-type VCO. The VCO occupies an area of  $150 \mu\text{m} \times 150 \mu\text{m}$ , consumes a dc power of 240 mW, exhibits a phase noise better than  $-87 \text{ dBc/Hz}$  at 1MHz offset and features a remarkably high ratio (25/45) of the VCO frequency to the process  $f_t$ .

### I. INTRODUCTION

Voltage controlled oscillators (VCOs) are widely used in many multi giga-bit per second systems, such as clock-data recovery and clock synthesizer PLLs. While most high frequency VCOs, reported in the literature, use some form of LC tank or resonator to achieve good phase noise performance [1], [2], they often occupy a large die area and have very limited tuning range. The VCO presented in this work is an inductorless ring-type oscillator implemented in a 45 GHz SiGe HBT technology and features a 25 GHz oscillation frequency, a relatively small area, a good tuning range and a phase noise performance comparable to recently reported resonator-type VCOs [1], [2].

### II. VCO DESIGN

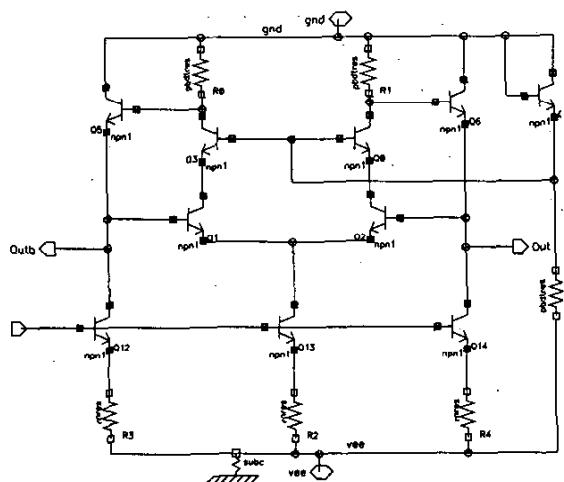

The VCO core used in this work, and shown in Fig. 1, is similar to the core oscillator previously proposed by the authors and implemented in InP HBT technology [3], [4]. In the circuit, a cascode amplifier is followed by an emitter follower in a closed loop, thus producing a single-stage ring oscillator. Bias currents are supplied by the current mirrors at the tail of each branch to set the operating points near the maximum  $f_t$  of the transistors. A change in input

bias voltage varies the bias currents and hence the oscillation frequency. To maintain the oscillation, Barkhausen's criteria must be met [4].

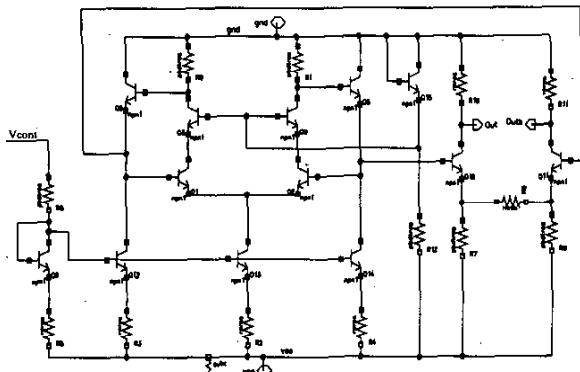

In the first step of the design, a 13 GHz differential VCO was developed from the core oscillator mentioned above. A voltage-to-current converter was added to the core oscillator, to control the current mirrors providing bias for different branches of the circuit. The complete schematic of the 13 GHz VCO, including an output buffer, is shown in Fig. 2. The resistors used in the current mirrors are chosen to optimize signal power and noise, while isolating the ac nodes of the VCO by increasing the impedance of the tail current sources. The output buffer is a differential pair with a gain designed to maximize signal to noise ratio at the output. The outputs of the differential pair buffer are terminated by  $50 \Omega$  resistors on chip. This leaves the emitter degeneration resistor, connecting the emitters of the output buffer transistors, as the main design parameter to control the gain of this stage. The degeneration resistor affects the gain, noise and linearity of this stage.

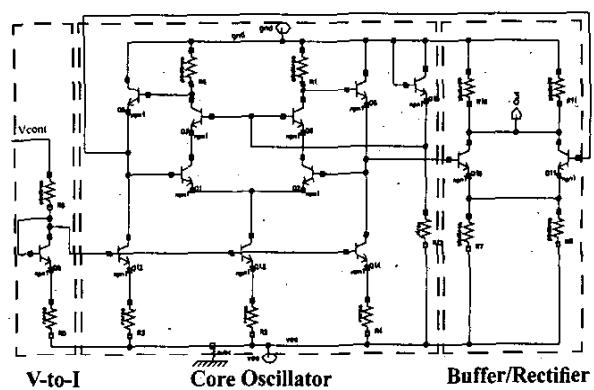

The 25 GHz VCO is in most parts similar to the 13 GHz VCO and the schematic is shown in Fig. 3. The core oscillator and the voltage-to-current converter are identical to those in the 13 GHz VCO. However, the buffer stage is modified in order to rectify the two differential signals from the core oscillator and sum up the two components so as to produce a single-ended output at double the frequency. The emitter degeneration of the buffer stage is removed in this case and the emitters of the differential pair transistors are connected together. As a result, the two base-emitter diodes and the two paralleled emitter bias resistors of the buffer stage form a full-wave rectifier. Since the inputs to this stage are complementary, the signal

generated at the emitter node, which is the resultant of the two emitter current components, has a frequency twice that at each base terminal. The collectors of the two transistors in the buffer stage are tied together to sum a copy of the emitter currents. While operating as a full-wave rectifier, the buffer stage also isolates the core oscillator from the load. The fundamental VCO frequency and its odd harmonics ( $f$ ,  $3f$ ,  $5f$ , ...) are suppressed by the symmetrical nature of the full-wave rectifier and its circuit implementation. The higher harmonics of the full-wave rectified signal ( $4f$ ,  $6f$ , ...) are also highly attenuated by the low-pass nature of the SiGe transistors which have an  $f_T$  of 45 GHz, leaving the  $2f$  component as the main output frequency.

### III. EXPERIMENTAL RESULTS

The 13 GHz VCO is fully differential and was implemented using a symmetrical layout to reduce the effect of common mode noise, substrate and supply noise. It occupies an area of  $150\mu\text{m} \times 150\mu\text{m}$ . The circuit was tested on wafer using 40 GHz probes and a 50 GHz spectrum analyzer. The measured results indicate that the frequency can be swept from about 8 GHz to above 13 GHz. Maximum dc power dissipation of this VCO is about 240 mW from a -3.3 V supply voltage. The power delivered at each output varies from -34 dBm up to about -4 dBm into a  $50\Omega$  load. The measured phase noise is -90 dBc/Hz @ 1MHz.

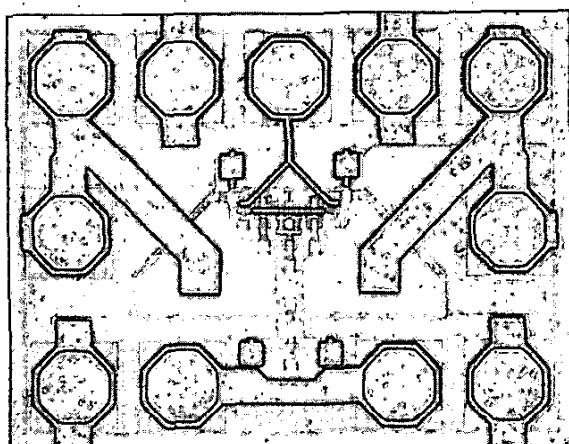

The micrograph of the SiGe 25 GHz VCO with built-in frequency doubler is shown in Fig. 4. The physical size of the circuit is nearly the same as that of 13 GHz VCO ( $150\mu\text{m} \times 150\mu\text{m}$ ). Although the circuit has a single-ended output, the internal circuitry is fully differential and the layout is symmetrical, thus reducing the effect of common mode noise. In addition, the circuit symmetry helps to suppress the fundamental core frequency and its odd harmonics in the frequency doubler.

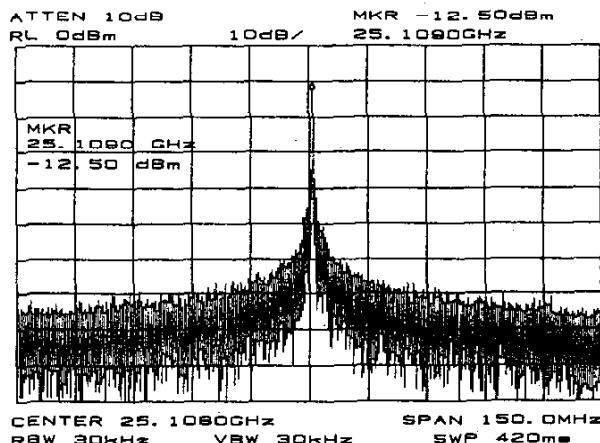

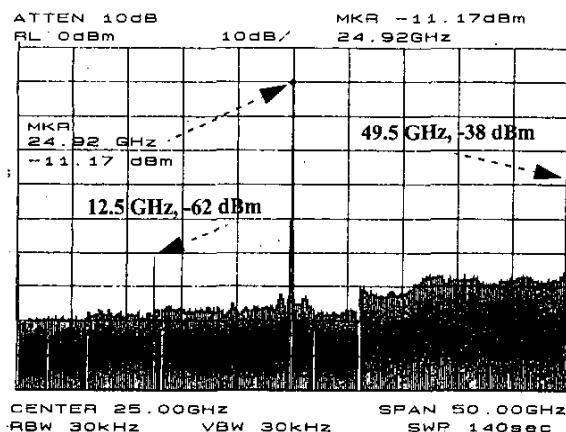

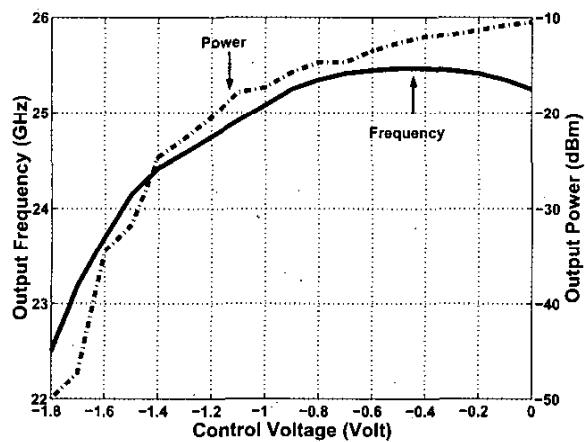

The circuit was tested by wafer probing. The near-carrier spectrum of the VCO oscillating at a frequency above 25 GHz is shown in Fig. 5. This circuit demonstrates a ratio of 0.56 (= 25/45) between VCO frequency and process  $f_T$ , a remarkably high ratio for a ring-type oscillator. As evident from the full spectrum of the VCO, depicted in Fig. 6, the core VCO frequency  $f$  was attenuated by about 50 dB compared to the desired output frequency  $2f$ . No frequency component was measurable at  $3f$  while the component at  $4f$ , within the 50 GHz range of the spectrum analyzer, was more than 20 dB below the  $2f$  component. As shown in Fig. 7, the frequency tuning range of this VCO is about 3

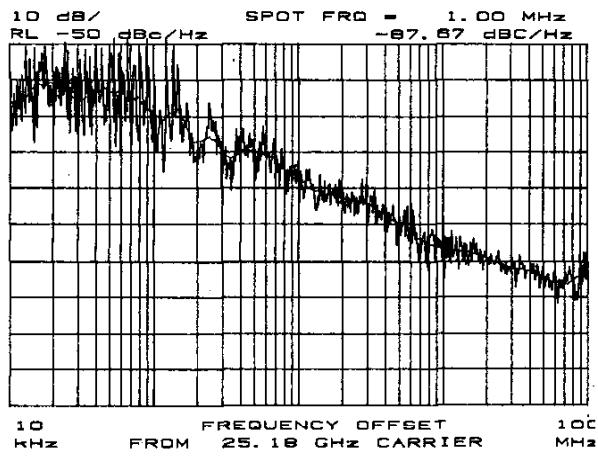

GHz, from 22.5 GHz to 25.5 GHz. The dc power dissipated by this VCO is approximately the same as that in the 13 GHz VCO and the output power varies from -50 to about -10 dBm over the tuning range, as shown in Fig. 7. The measured phase noise is below -87 dBc/Hz @ 1 MHz offset, as shown in Fig. 8. This value is about 3 dB better than expected in practice (note that a phase noise measurement at the 2nd harmonic automatically implies  $20\log(2) = 6$  dB baseline degradation [5]). The relative phase noise improvement of the 25 GHz VCO (over the 2nd harmonic of the 13 GHz VCO) is largely due to the conversion gain (differential to single-ended) of the output buffer; with both collector currents going on to the same equivalent load resistor the total signal power is now delivered on one output, rather than two. In addition, the removal of the emitter degeneration resistor reduces noise at the output stage. The gain of the VCO is approximately 2 GHz/V around 25 GHz frequency.

### IV. CONCLUSION

Design and implementation of a 25 GHz inductorless VCO in a 45 GHz SiGe technology, was demonstrated. A full-wave rectification scheme was used to double the frequency of a 13 GHz VCO and achieve the 25 GHz VCO with a tuning range of 3 GHz. The technique results in a ratio of 25/45 of the VCO frequency to the  $f_T$  of the technology: one of the highest such ratio ever reported for a ring-type oscillator. The layout of the VCO is symmetrical to improve phase noise performance, and the circuit occupies an area of  $150\mu\text{m} \times 150\mu\text{m}$ . Power consumption from -3.3 V supply is less than 250 mW, and measured phase noise at 1 MHz offset to the respective carrier is -87 dBc/Hz.

### ACKNOWLEDGMENTS

The authors acknowledge the financial support of NSERC, Micronet, Gennum, Nortel Networks, PMC-Sierra and Zarlink. The fabrication was carried out through the Canadian Microelectronics Corporation.

### REFERENCES

- [1] K. Ettinger, A. Stelzer, C. G. Diskus, W. Thomann, J. Fenk and R. Weigel, "Single-chip 20-GHz VCO and Frequency Divider in SiGe Technology", IEEE Microwave Symposium, Digest, Vol. 2, pp. 835-838, 2002.

- [2] S. Subbanna, R. Groves, B. Jagannathan, D. Greenberg, G. Freeman, E. Eld, R. Volalnt, D. Ahlgren, B. Martin, K. Stein, D. Herman and B. Meyerson, "Using Silicon-Germanium mainstream BICMOS technology for X-band and LMDS (25-30 GHz) Microwave applications", IEEE

Microwave Symposium, Digest, Vol. 1, pp. 401-404, 2002.

- [3] H. Djahanshahi, N. Saniei, S.P. Voinigescu, M.C. Maliepaard and C.A.T. Salama, "20-GHz InP-HBT voltage-controlled oscillator with wide tuning range", RFIC Symposium, Digest, pp. 161-164, 2001.

- [4] H. Djahanshahi, N. Saniei, S.P. Voinigescu, M.C. Maliepaard and C.A.T. Salama, "A 20-GHz InP-HBT voltage-controlled oscillator with wide frequency tuning range", *IEEE Trans. on Microwave Theory and Techniques*, Vol. 49, pp. 1566-1572, 2001.

- [5] A. Hajimiri and T. H. Lee, "A general theory of phase noise in electrical oscillators", *IEEE J. Solid-State Circuits*, Vol. 33, pp. 179-194, 1998.

Fig. 1. Schematic of the Core VCO [4].

Fig. 2. Schematic of the 13 GHz VCO.

Fig. 3. Schematic of the 25 GHz VCO.

Fig. 4. Micrograph of the 25 GHz VCO.

Fig. 5. VCO Frequency Characteristics, Spectrum near 25 GHz

Fig. 6. VCO Frequency Characteristics, Full spectrum depicting various harmonics.

Fig. 7. Characteristics of the 25 GHz VCO.

Fig. 8. Phase noise of the 25 GHz VCO.